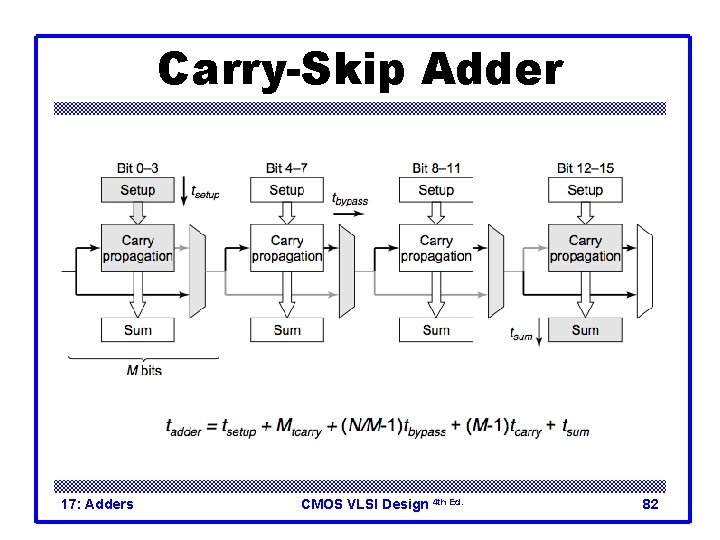

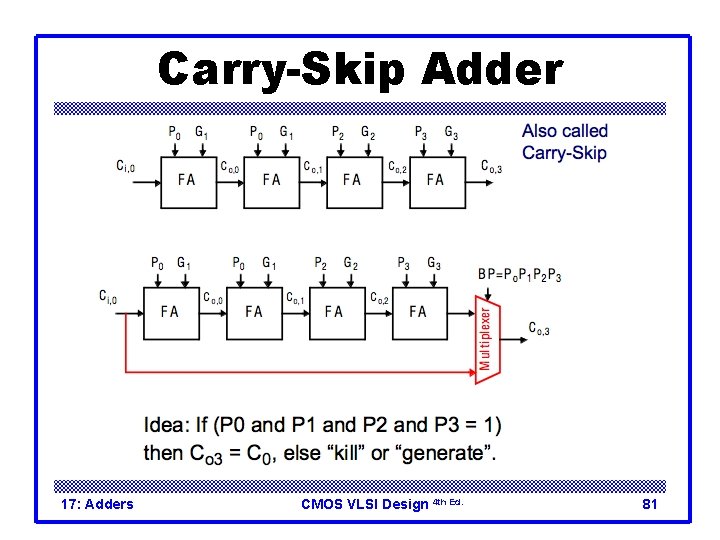

Design of Adders Jacob Abraham September 22 2020 14 31 Carry-Skip Adder Carry-ripple is slow through all N stages Carry-skip allows carry to skip over groups of n bits Decision based on n-bit propagate signal. A Layout Diagram b Analog Simulation of. Adders in vlsi design.

Adders In Vlsi Design, Hence the economics of VLSI are attractive only when a large number eg tens of thousands or more of units of each type can be used. Datapath Carry-Skip Adder ci4 4-bit adder A carry-skip adder is designed to speed up a wide adder by aiding the propagation of a carry bit around a portion of the entire adder. Information is not lost in reversible gates and back computation is possible in reversible circuits with reduced power dissipation. Design of Adders Jacob Abraham September 22 2020 14 31 Carry-Skip Adder Carry-ripple is slow through all N stages Carry-skip allows carry to skip over groups of n bits Decision based on n-bit propagate signal.

Figure 16 Performance Analysis Of High Speed Hybrid Cmos Full Adder Circuits For Low Voltage Vlsi Design From hindawi.com

Figure 16 Performance Analysis Of High Speed Hybrid Cmos Full Adder Circuits For Low Voltage Vlsi Design From hindawi.com

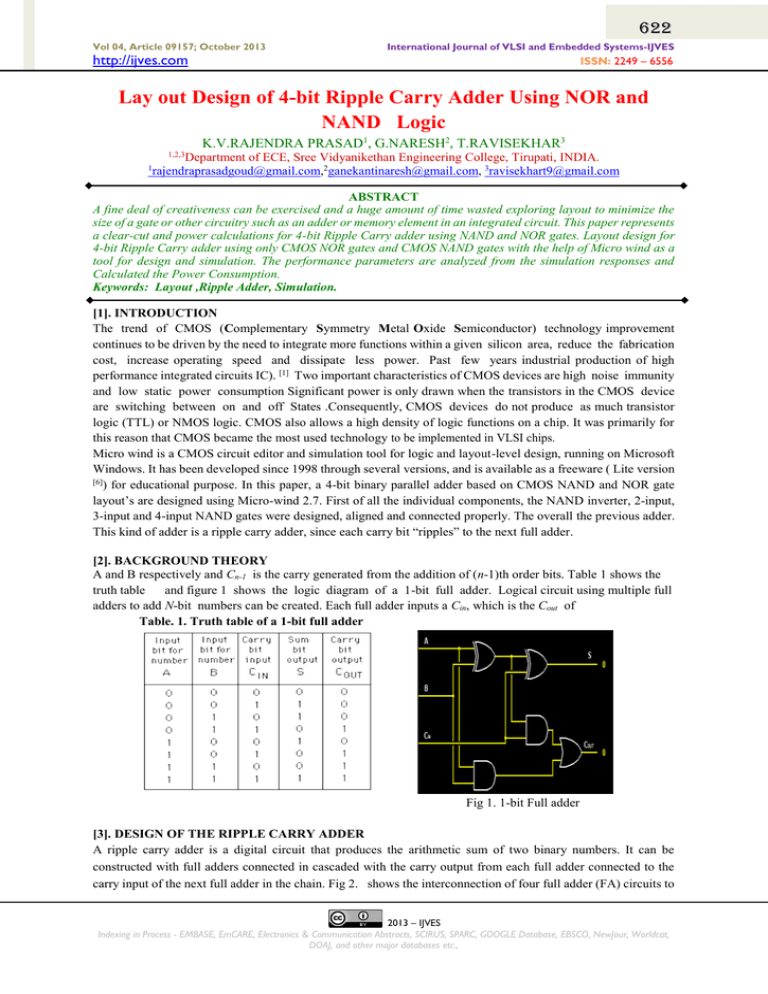

The microprocessor is a VLSI device. Jin-Fu Li EE NCU 21 ii3 ci4 c iP ii3 Carry-skip Carry-skip logic Generalization. ADDAiBiCINSiCOUT How do we build a 4-bit ripple carry adder. Of ECE Adhiparasakthi Engineering College MelmaruvathurTamilNadu India.

By using both adders we can implement ripple carry adder using ripple carry adder we can perform addition for any number of bits.

Read another article:

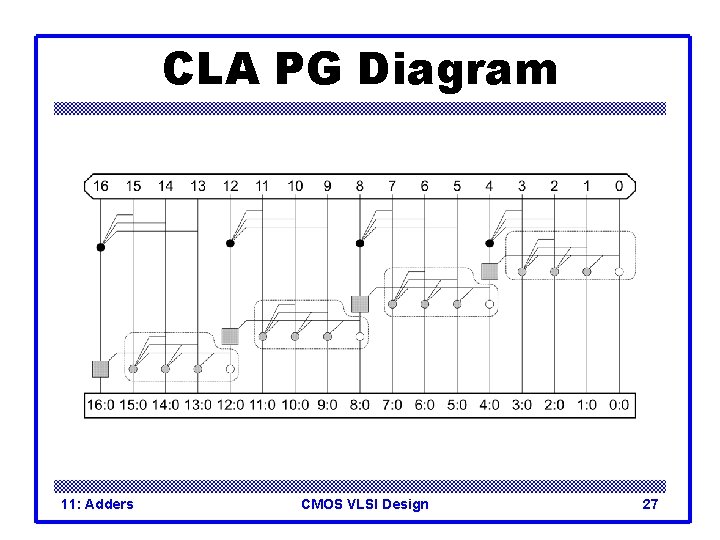

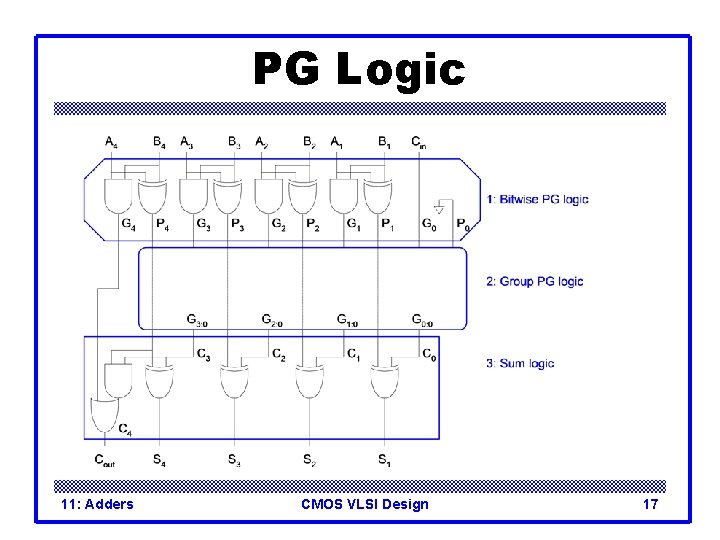

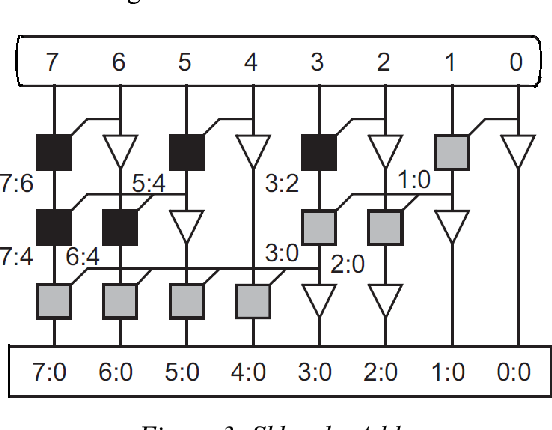

Henceforth this adder shall be referred to as the DSSC_HE adder dual sum single carry heterogeneously encoded adder. We use adders frequently in digital design and VLSI designs in digital design we use adders such as half adder full adder. Sp09 CMPEN 411 L20 S1 CMPEN 411 VLSI Digital Circuits Spring 2009 Lecture 20. VLSI Design Fall 2020 8. Design of Adders 8 PG Diagram Notation ECE Department University of Texas at Austin Lecture 8.

Source: semanticscholar.org

Source: semanticscholar.org

The second problem is the development of unique VLSI devices. PC with Windows XP. By using both adders we can implement ripple carry adder using ripple carry adder we can perform addition for any number of bits. 24 Carry-Select Adder Trick for critical paths dependent on late input X Precompute two possible outputs for X 0 1 Select proper output when X arrives Carry-select adder precomputes n-bit sums For both possible carries into n-bit group C in A 41 B 41 S 41 C 4 0 1 A 85 B 85 S 85 C 8 0 1 A 129 B 129. Pdf 4 Bit Fast Adder Design Topology And Layout With Self Resetting Logic For Low Power Vlsi Circuits Semantic Scholar.

Source: slidetodoc.com

Source: slidetodoc.com

The microprocessor is a VLSI device. I3 i ci P k-bit adder c ci ik Advanced Reliable Systems ARES Lab. Henceforth this adder shall be referred to as the DSSC_HE adder dual sum single carry heterogeneously encoded adder. Operation of a Full Adder is defined by the Boolean equations for the sum and carry signals. Introduction To Cmos Vlsi Design Lecture 11 Adders.

Source: hindawi.com

Source: hindawi.com

Very-large-scale integration VLSI is the process of creating an integrated circuit IC by combining thousands of transistors into a single chip. In producing a VLSI device the design costs are extremely high but the production cost per unit is extremely low. Sp09 CMPEN 411 L20 S1 CMPEN 411 VLSI Digital Circuits Spring 2009 Lecture 20. It is a serial adder. Figure 8 Performance Analysis Of High Speed Hybrid Cmos Full Adder Circuits For Low Voltage Vlsi Design.

Source: studylib.net

Source: studylib.net

Suppose we want to design a Full Adder FA. It has a huge delay problem. Datapath Carry-Skip Adder ci4 4-bit adder A carry-skip adder is designed to speed up a wide adder by aiding the propagation of a carry bit around a portion of the entire adder. VLSI Design Fall 2020 8. Lay Out Design Of 4 Bit Ripple Carry Adder Using Nor And.

Source: slidetodoc.com

Source: slidetodoc.com

We use adders frequently in digital design and VLSI designs in digital design we use adders such as half adder full adder. Information is not lost in reversible gates and back computation is possible in reversible circuits with reduced power dissipation. In producing a VLSI device the design costs are extremely high but the production cost per unit is extremely low. PC with Windows XP. Introduction To Cmos Vlsi Design Lecture 11 Adders.

Source: slidetodoc.com

Source: slidetodoc.com

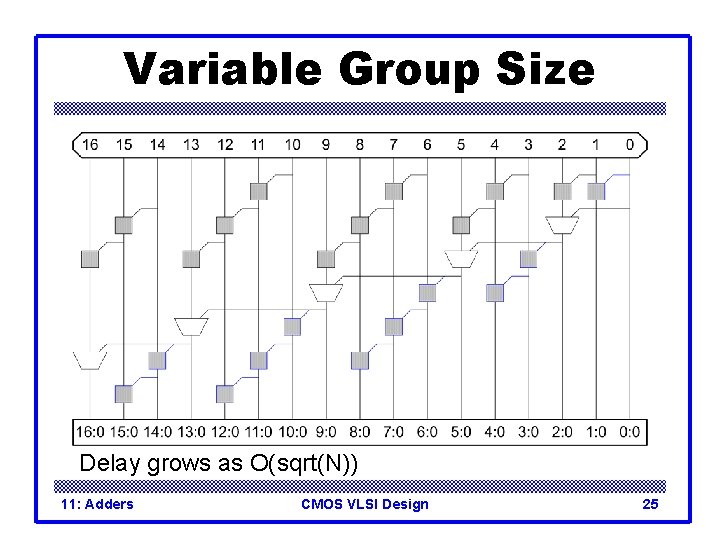

Hence the economics of VLSI are attractive only when a large number eg tens of thousands or more of units of each type can be used. Actual Design Steps 3 adder architecture configuration and selection of the prediction table 4 column selection in the prediction table and truth table generation 5 generation of the test addition set through and truth table 6 synthesis and circuit design of the prediction logic three stages from and Truth Table 7 adder circuit design through standard full-custom VLSI. 24 Carry-Select Adder Trick for critical paths dependent on late input X Precompute two possible outputs for X 0 1 Select proper output when X arrives Carry-select adder precomputes n-bit sums For both possible carries into n-bit group C in A 41 B 41 S 41 C 4 0 1 A 85 B 85 S 85 C 8 0 1 A 129 B 129. PG Student VLSI design Department. Lecture 17 Adders Outline Q Q Q Q.

Source: slidetodoc.com

Source: slidetodoc.com

The 74x85 4-bit comparator and the 74x283 4-bit adder are examples of MSI circuits that can be used as the individual modules in a larger iterative circuit. To design and construct half adder full adder half subtractor and full subtractor circuits and verify the truth table using logic gates. 24 Carry-Select Adder Trick for critical paths dependent on late input X Precompute two possible outputs for X 0 1 Select proper output when X arrives Carry-select adder precomputes n-bit sums For both possible carries into n-bit group C in A 41 B 41 S 41 C 4 0 1 A 85 B 85 S 85 C 8 0 1 A 129 B 129. ADDAiBiCINSiCOUT How do we build a 4-bit ripple carry adder. Lecture 17 Adders Outline Q Q Q Q.

Source: researchgate.net

Source: researchgate.net

In designing of Full adder XOR gate plays an important role as using it performance of the full adder can be improved. Hence the economics of VLSI are attractive only when a large number eg tens of thousands or more of units of each type can be used. A b Fig -5a-b. Actual Design Steps 3 adder architecture configuration and selection of the prediction table 4 column selection in the prediction table and truth table generation 5 generation of the test addition set through and truth table 6 synthesis and circuit design of the prediction logic three stages from and Truth Table 7 adder circuit design through standard full-custom VLSI. A Layout Of Design 1 13t Full Adder Cell B Layout Of Design 2 Download Scientific Diagram.

Source: slidetodoc.com

Source: slidetodoc.com

The half adder consists of two input variables designated as Augends and Addend bits. Reversible full adder circuits are implemented in the previous work to optimize the design and speed of the circuits. The second problem is the development of unique VLSI devices. Of ECE Adhiparasakthi Engineering College MelmaruvathurTamilNadu India. Introduction To Cmos Vlsi Design Lecture 11 Adders.

Source: hindawi.com

Source: hindawi.com

Design of Adders Jacob Abraham September 22 2020 14 31 Carry-Skip Adder Carry-ripple is slow through all N stages Carry-skip allows carry to skip over groups of n bits Decision based on n-bit propagate signal. Of the parallel prefix adders is that its ability to compute addition operation with a significantly high speed reliability and efficiency in the category of Very Large Scale Integration VLSI. First we will examine a realization of a one-bit adder which represents a basic building block for all the more elaborate addition schemes. It is a serial adder. Figure 16 Performance Analysis Of High Speed Hybrid Cmos Full Adder Circuits For Low Voltage Vlsi Design.

Source: slidetodoc.com

Source: slidetodoc.com

Multipliers in VLSI 1. Since adders are basic block of VLSI and DSP applications it is very important to design adders that occupy minimum area and reduced power consumption. VLSI Design - Digital System. The half adder consists of two input variables designated as Augends and Addend bits. Introduction To Cmos Vlsi Design Lecture 11 Adders.

Source: semanticscholar.org

Source: semanticscholar.org

Jin-Fu Li EE NCU 21 ii3 ci4 c iP ii3 Carry-skip Carry-skip logic Generalization. Multiplier Design Adapted from Rabaeys Digital Integrated Circuits Second Edition 2003 J. We use adders frequently in digital design and VLSI designs in digital design we use adders such as half adder full adder. Algorithms and VLSI Implementation. Performance Analysis Of Parallel Prefix Adder For Datapath Vlsi Design Semantic Scholar.

Source: hindawi.com

Source: hindawi.com

In producing a VLSI device the design costs are extremely high but the production cost per unit is extremely low. Tutorial On CMOS VLSI Design of Full Adder Day On My Plate - YouTube. The microprocessor is a VLSI device. Basic Full Adder Based Comparator The layout design of the basic full adder based comparator is shown in figure 5a and its analog simulation in figure 5b. Figure 1 Performance Analysis Of High Speed Hybrid Cmos Full Adder Circuits For Low Voltage Vlsi Design.

Source: slidetodoc.com

Source: slidetodoc.com

Suppose we want to design a Full Adder FA. Area Efficient Self Timed Adders For Low Power Applications in VLSI. A Layout Diagram b Analog Simulation of. Multiplier Design Adapted from Rabaeys Digital Integrated Circuits Second Edition 2003 J. Lecture 17 Adders Outline Q Q Q Q.

Source: slidetodoc.com

Source: slidetodoc.com

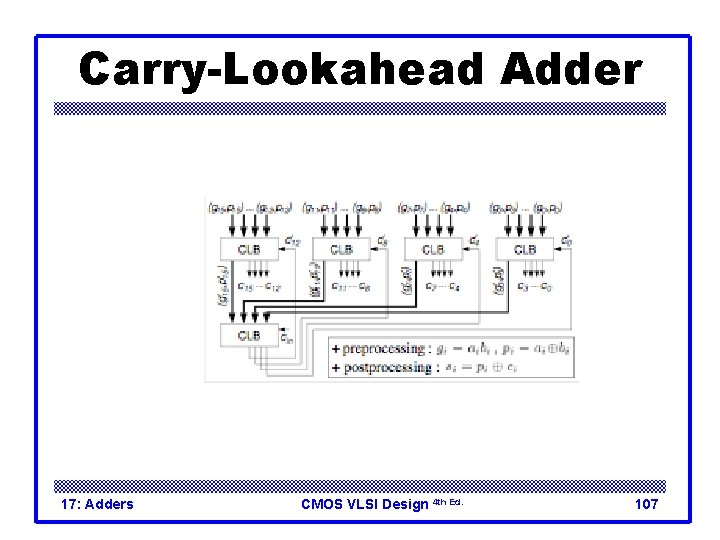

The carry-lookahead and the proposed carry-increment adders show the best overall performance characteristics for cell-based design. Jin-Fu Li EE NCU 21 ii3 ci4 c iP ii3 Carry-skip Carry-skip logic Generalization. I3 i ci P k-bit adder c ci ik Advanced Reliable Systems ARES Lab. It has a huge delay problem. Lecture 17 Adders Outline Q Q Q Q.