Asynchronous FIFO Verilog Code. FIFO First in First Out are commonly used for synchronizing across two process and when you need a temporary storage. Asynchronous fifo design verilog code.

Asynchronous Fifo Design Verilog Code, 4 Date. Edit save simulate synthesize SystemVerilog Verilog VHDL and other HDLs from your web browser. High when FIFO is empty else low. Asynchronous FIFO w 2 asynchronous clocks.

Verilog Code For Counter Verilog Code For Counter With Testbench Verilog Code For Up Counter Verilog Code For Down Counter Ve Coding Counter Counter Counter From pinterest.com

Verilog Code For Counter Verilog Code For Counter With Testbench Verilog Code For Up Counter Verilog Code For Down Counter Ve Coding Counter Counter Counter From pinterest.com

FIFO means first in first out. This implementation is based on the article 6 Asynchronous FIFO in Virtex-II FPGAs 7 writen by Peter. The Data width is 8 bits and FIFO Depth is 23 8. Scholar in VLSI DESIGN Electronics and Communication Engineering Department 2AssProfessor Electronics and Communication Engineering Department 1 2 GNANAMANI COLLEGE OF TECHNOLOGY NAMAKKAL TAMILNADU.

In synchronous fifo there may be 1 or 2 clocks since some FIFOs have separate clocks for read and write.

Read another article:

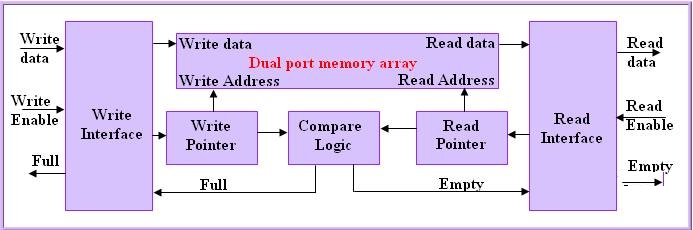

The Verification Env can be built around it in SV or UVM. NEW ASYNCHRONOUS FIFO DESIGN Asynchronous FIFO - General Working Verilog code for Asynchronous FIFO. A FIFO is a convenient circuit to exchange data between two clock domains. In synchronous fifo there may be 1 or 2 clocks since some FIFOs have separate clocks for read and write. 1 2 Function.

Verilog code for asynchronous FIFO. Answer 1 of 3. It manages the RAM addressing internally the clock domain crossing and informs the. Verilog Code for Async FIFO. Github Jagannaths3 Async Fifo Synthesizable Asynchronous Fifo Verilog Code.

Source: verilogpro.com

Source: verilogpro.com

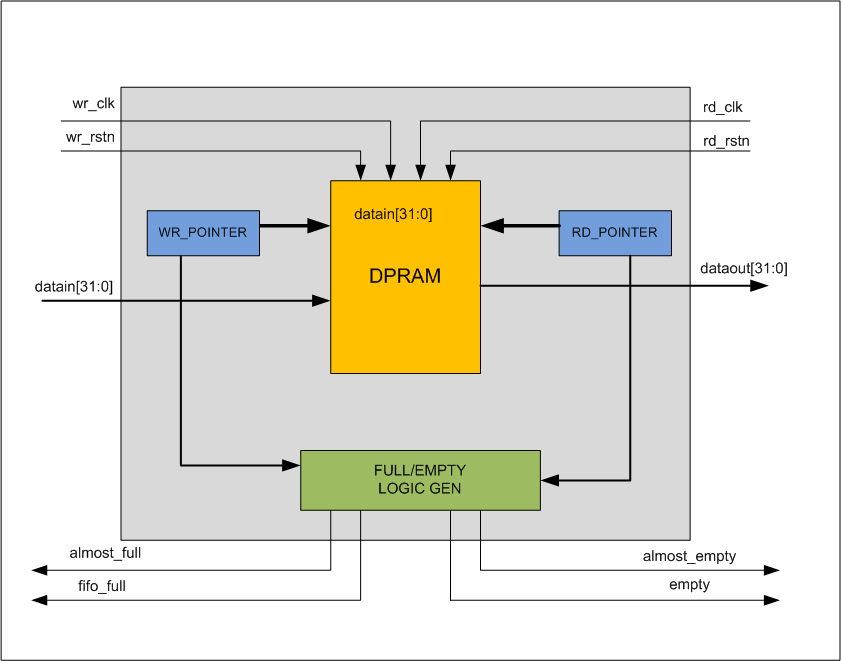

———-Abstract -FIFO is an approach for handling program work. An Asynchronous FIFO Design refers to a FIFO Design where in the data values are written to the FIFO memory from one clock domain and the data values are read from a different clock domain where in the two clock domains are Asynchronous to each other. Asynchronous FIFO Design. The figure-1 depicts asynchronous FIFO design. Dual Clock Asynchronous Fifo In Systemverilog Verilog Pro.

5 Notes. Verilog Code for Async FIFO. Scholar in VLSI DESIGN Electronics and Communication Engineering Department 2AssProfessor Electronics and Communication Engineering Department 1 2 GNANAMANI COLLEGE OF TECHNOLOGY NAMAKKAL TAMILNADU. The general block diagram of asynchronous FIFO is shown in Figure 1. Crossing Clock Domains With An Asynchronous Fifo.

Source: rtldigitaldesign.blogspot.com

Source: rtldigitaldesign.blogspot.com

NEW ASYNCHRONOUS FIFO DESIGN Asynchronous FIFO - General Working Verilog code for Asynchronous FIFO. The Verification Env can be built around it in SV or UVM. This implementation is based on the article 6 Asynchronous FIFO in Virtex-II FPGAs 7 writen by Peter. Asynchronous FIFO w 2 asynchronous clocks. Digital Design Expert Advise Asynchronous Fifo With Programmable Depth.

Source: fpga4student.com

Source: fpga4student.com

Verilog Code for Async FIFO. Synchronous FIFO Design Verilog code. Asynchronous FIFO w 2 asynchronous clocks. Here is the block diagram for Asynchronous FIFO. Verilog Code For Fifo Memory Fpga4student Com.

Source: researchgate.net

Source: researchgate.net

A method for organizing and manipulating a data buffer. In synchronous fifo there may be 1 or 2 clocks since some FIFOs have separate clocks for read and write. Scholar in VLSI DESIGN Electronics and Communication Engineering Department 2AssProfessor Electronics and Communication Engineering Department 1 2 GNANAMANI COLLEGE OF TECHNOLOGY NAMAKKAL TAMILNADU. Verilog code for asynchronous FIFO is given below. Fifo Is Going Full Because The Wptr Trails The Rptr By One Quadrant If Download Scientific Diagram.

———-Abstract -FIFO is an approach for handling program work. The Data width is 8 bits and FIFO Depth is 23 8. Create a normal memory in Verilog. Asynchronous FIFO design using verilog. Async Fifo In Verilog Development Log.

Source: verilogpro.com

Source: verilogpro.com

The Data width is 8 bits and FIFO Depth is 23 8. Asynchronous FIFO w 2 asynchronous clocks. Asynchronous FIFO Design 21 Introduction. This page covers Asynchronous FIFO verilog code and mentions Asynchronous FIFO test bench script. Dual Clock Asynchronous Fifo In Systemverilog Verilog Pro.

Source: youtube.com

Source: youtube.com

3 Coder. Asynchronous FIFO design using verilog. ASYNCHRONOUS FIFO DESIGN USING VERILOG Lincy DF1 SThenappan2 1PG. Rev 12 Asynchronous FIFO Design 2 10 Introduction An asynchronous FIFO refers to a FIFO design where data values are written to a FIFO buffer from one clock domain and the data values are read from the same FIFO buffer from another clock domain where the two clock domains are asynchronous to. Verilog On Intel Altera Fpga Lesson 10 Fifo 02 Synchronous Fifo 01 Youtube.

Source: youtube.com

Source: youtube.com

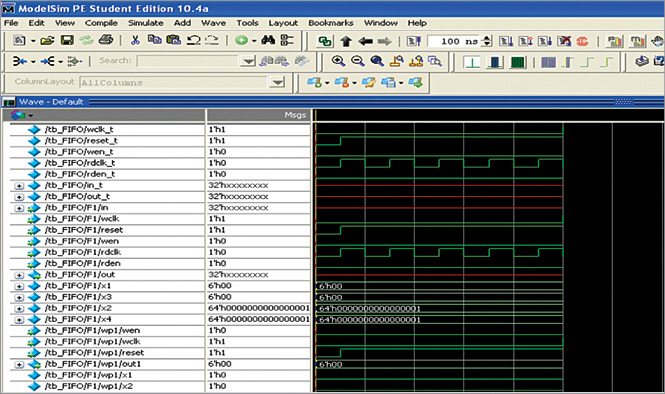

INTRODUCTION FIFO First In First Out is a buffer that stores data in a way. It mentions simulated output of Asynchronous FIFO verilog code. What you are looking at here is whats called a dual rank synchronizer. In this project Verilog code for FIFO memory is presented. What Is Asynchronous Fifo Asynchronous Fifo Design Clock Domain Crossing Explained In Detail Youtube.

Source: semanticscholar.org

Source: semanticscholar.org

1 Points Download Earn points. 3 Coder. Scholar in VLSI DESIGN Electronics and Communication Engineering Department 2AssProfessor Electronics and Communication Engineering Department 1 2 GNANAMANI COLLEGE OF TECHNOLOGY NAMAKKAL TAMILNADU. Asynchronous FIFO Design. Designing Of 8 Bit Synchronous Fifo Memory Using Register File Semantic Scholar.

4 Date. Asynchronous FIFO Verilog Code. To do so well build off of our previous work using 2FF or 3FF synchronizers but this time well need to introduce Gray codes as well. The Verification Env can be built around it in SV or UVM. Digital Design Expert Advise Asynchronous Fifo With Programmable Depth.

Source: electrosofts.com

Source: electrosofts.com

The figure-2 depicts simulation output of Asynchronous FIFO logic shown in figure-1 above. It mentions simulated output of Asynchronous FIFO verilog code. Rev 12 Asynchronous FIFO Design 2 10 Introduction An asynchronous FIFO refers to a FIFO design where data values are written to a FIFO buffer from one clock domain and the data values are read from the same FIFO buffer from another clock domain where the two clock domains are asynchronous to. This implementation is based on the article 6 Asynchronous FIFO in Virtex-II FPGAs 7 writen by Peter. Fsm Design Using Verilog Asicguide Com.

Source: github.com

Source: github.com

If appropriate precautions are not taken then we could end up in a scenario where write into FIFO has not yet finished and we are attempting to Read it or Vice-versa. FIFO First in First Out are commonly used for synchronizing across two process and when you need a temporary storage. And its verilog test bench code are already given in previous posts. Let us have a small recap of asynchronous FIFO working and then we will go to new asynchronous FIFO design. Github Teekam Chand Khandelwal Asynchronous Fifo Asynchronous Fifo Using Verilog And Testbench Using System Verilog For Asynchronous Fifo Design In Different Module.

Source: electronicsforu.com

Source: electronicsforu.com

Synchronous FIFO Design Verilog code. Asynchronous FIFO design using verilog. A FIFO is a convenient circuit to exchange data between two clock domains. The figure-2 depicts simulation output of Asynchronous FIFO logic shown in figure-1 above. Fifo Design Using Verilog Detailed Project Available.